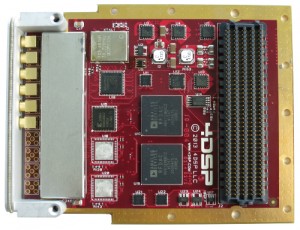

2-Channel DAC FMC module – High-Pin-Count

The FMC230 is a dual channel DAC FMC with a very wide band. The two 14-bit D/A channels operate at 5.7Gsps (2.85Gsps direct RF synthesis) and are clocked by either an internal clock source (optionally locked to an external reference) or an externally supplied sample clock. In addition, a trigger input for customized sampling control is available to users. The FMC230 daughter card is mechanically and electrically compliant to the FMC standard (ANSI/VITA 57.1).

The FMC230 has a high-pin count connector, front panel I/O, and can be used in a conduction cooled environment. The design is based on Analog Devices’ AD9129 single channel 14-bit 5.7Gsps Digital-to-Analog converter. The analog signals are AC coupled connecting to MMCX or SSMC coax connectors on the front panel.

The FMC230 allows flexible control on clock source and D/A features through serial communication busses. Furthermore the card is equipped with power supply and temperature monitoring and offers several power-down modes to switch off unused functions in order to reduce system level power consumption. It is well suited for low power applications such as airborne where the highest level of performance is required while ensuring that mission range does not get affected.

Features:

- Two AD9129: 2-channel 14-bit D/A up to 5.7 Gsps (2.85Gsps without 1:2 interpolation) – LVDS

- VITA 57.1-2010 compliant

- Conduction Cooled – Standard Option

- Single ended AC-coupled analog signals.

- 6 MMCX/SSMC connectors available from the front panel

- Clock Source, Sampling Frequency, and Calibration through a SPI communication busses

- Flexible clock tree enables:

- on board VCO: 2300MHz – 2650MHz

- external reference clock

- external sampling clock

- Power-down modes to switch off unused functions for system power savings

- Mil-I-46058c Conformal Coating Compliant (optional)

- HPC – High Pin Count Connector

- LVDS IO signalling